基于DSP的高速PCB抗干扰设计(二)

另外在输入端或电池供电的地方加上高频是非常有利的。一般情况下,对退耦的取值不是很严格,一般按C=l/,计算,即为10 M时取0.1μF的电容。

(5) 的布局

在进行系统开发时,电源需要慎重考虑。因为一些电源芯片发热量很大,应优先安排在利于散热的位置,要与其他元器件隔开一定距离。可以利用加散热片或在器件下面铺铜来进行散热处理。注意在开发板底层不要放置发热组件。

(6) 其他注意

对于DSP系统其他组件的布局应该尽量考虑到方便、调试方便和美观等要求。如对电位器、可调线圈、可变电容器、拨码开关等可调器件要结合整体结构放置。对于超过15 g的器件要加固定支架再焊接,特别注意要留出的定位孔及固定支架所占用的位置。PCB边缘的元器件离PCB板边距离一般不要小于2 mm,PCB最好为矩形,长宽比为3:2或4;3。

2.3布线设计

在综合考虑到增加DSP系统抗干扰性,增强能力进行布局后,布线也要有一些措施和技巧。

(1) DSP的布线

布线大体上是从核心器件开始,并以其为中心展开。对于DSP这种P(Plast Quad FIat k)或(BaIl Grid Arrayr)封装的器件,如图3所示,应先根据SRAM、Flash和CPLD的布局位置大体判断出走线方向,对引脚进行扇出(fanout)操作。特别是对于Q&BGA类型的器件,扇出就显得尤其重要。在布线开始之初,就先把BGA类型器件的引脚作扇出,可以为后面的布线节省时间,并可以提高布线的质量和效率。在布线时,合理利用工具的特点,比如power PCB的dynami rou-ting,可以最优计划空间。用dynamic的时候,这个功能会自动让线与线之间的空间保持在规则里面,不浪费空间,减少后续修改,提高布线的质量和效率。

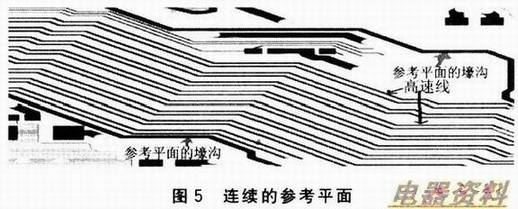

对于高速DSP还要注意串扰及蛇行(delay tune)走线处理。蛇行走线处理,如图4所示,可以保证信号的完整性,还要保证高速信号参考平面的连续性。在需要作平面分割的时候,一定注意不要让高速线跨不连续的平面;非要跨,就加跨平面的电容,如图5所示。