基于DSP的高速PCB抗干扰设计(三)

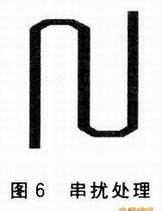

当信号线(trace)间隔3倍信号线宽时,信号间相互串扰(coupling)的几率只有25%左右,这样就可以达到抗电磁干扰()的要求。所以,像CLK和SRAM这些高速信号线,切记与它旁边的信号线远离3倍宽以上,调等长时,即蛇型走线,线与线的宽度也要3倍信号线宽以上,包括对于其本身的信号线也要3倍信号线宽。如图6所示,线宽5 mil*,绕线本身内部的距离是15mil,大于等于3倍的线宽。

(2) 时钟的布线

对于时钟信号,要使其对于其他信号的走线距离尽量大,保证在4倍线宽以上的距离,并且在时钟(零件)的下面不要走线;对于模拟输入线,参考电压端和I/0信号线尽量远离时钟。

(3) 对系统的处理

是系统中最重要的部分。在的层叠设计中分配了单独的电源层,但由于一个系统有多种数字和模拟器件,这样所用到的电源也有多种,所以对电源层进行了分割,使相同电源特性的器件分割在同一区域内,可就近连接到电源层。但要特别注意,进行分割的时候要注意使参考电源平面的信号连续。经过实验证明,40 mil的线宽,可以通过的能保证有l A;对于过孑L,钻径为16 mil的可以通过1 A的电流,所以对于DSP系统,电源线大于20 mil即可。对于电源线上的电磁辐射防护要注意以下几点:

◆用旁路限制板上交流电流的泄漏;

◆在电源线上串接共模扼流圈(common modechoke),以抑制流经线中的共模电流;

◆布线靠近,减小磁辐射面积。

(4) 对接地的处理

在所有的问题中,主要问题都是不适当的接地而引起的。地线处理的好坏直接影响系统的稳定可靠。接地有以下作用:

◇降低输出线上的共模电压VCM;

◇减小对静电(ESD)的敏感;

◇减小电磁辐射。

高频数字电路和低频模拟电路的地回路绝对不能混合,必须将数/模地分开,因为数字电路高低电位切换时会在电源和地产生;若地平面不分开,模拟信号依然会被地噪声干扰。所以对高频信号应采用多点串联接地,尽量加粗缩短地线,这样除减小压降外,更重要的是降低耦合噪声。但对于一个系统而言,无论怎样分,最终的大地只有一个,只是泻放途径不同而已,所以最后通过磁珠或0 n,将数字地和模拟地连在一起来消除混合信号的干扰。

地平面分割时,必须保证参考平面的连续性。像数/模共存的PCB板,若模拟信号线走的距离比较远,应尽量使其参考回流路径也是模拟地。这意味着在地层要沿模拟信号的路径割一个模拟地,使其参考模拟地,保证其参考平面的连续性。

(5) 其他注意事项

①在布线时,导线的拐角处一般不要走成90°折线,以减小高频信号对外的发射耦合。

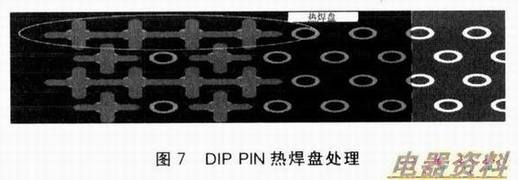

②对PCB铺铜时,尽量避免使用大面积铜箔,否则经过长时间受热,易发生铜箔脱落现象;必须用大面积铜箔的时候可以用栅格替代,这样有利于排除铜箔与基板之间粘合剂受热产生挥发性气体。在贯穿的零件脚上()铺的铜箔最好也用热焊盘(thermal)处理;应避免虚焊,提高良品率,如图7所示。

③输入与输出的边线应避免相临平行,以避免产生反射干扰;必要时加地线隔离。两相邻层的布线要互相垂直,平行容易产生耦合。

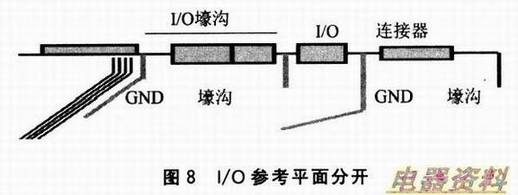

④对于I/0,最好能够把各自参考平面的不同区域分割开,使不同的I/O信号不会相互之间干扰,如图8所示。

结 语

本文先通过对DSP系统所受到的干扰进行分析,找出可能产生干扰的主要原因,然后针对各种原因,利用PCB板的层叠式设计、器件布局以及详细的布线方法,从各个方面将DSP系统可能产生的干扰减到最小。文中各种减小干扰的方法已经应用于实际的DSP系统的开发(TI公司的DSP芯片TMS320LF2407),其效果良好。

- 上一篇:高速DSP系统PCB板的可靠性设计

- 下一篇:基于DSP的高速PCB抗干扰设计(二)