EPROM和RAM综合扩展的硬件接口电路

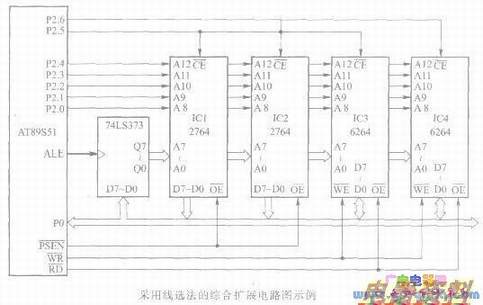

例1:采用线选法扩展2片8KB的RAM和2片8 KB的EPROM。RAM芯片选用2片6264。扩展2片EPROM芯片,选用2764。硬件接口如下图所示。

(1)控制信号及片选信号。 地址线P2.5直接接到l(2764)和IC3(6264)的片选CE(的反)端,P2.6直接接到IC2(2764)和IC4(6264)的片选CE(的反)端。当P2.6=0,P2.5=1时,IC2和IC4的片选端CE(的反)为低,IC1和IC3的CE(的反)端全为高电平。当P2.6=1,P2.5=0时,IC1和IC3的CE(的反)端都是低电平,每次同时选中两个芯片,具体对哪个芯片进行读/写操作还要通过PSEN(的反)、WR(的反)、RD(的反)控制线来控制。当PSEN(的反)为低电平时,到片外程序存储区EPROM中读程序;当读/写信号RD或WR为低电平时,则对片外RAM读数据或写数据。PSEN(的反)、WR(的反)、RD3(的反)个信号是在执行指令时产生的,任意时刻只能执行一条指令,所以只能有一个信号有效,不可能同时有效,所以不会发生数据冲突。

(2)各芯片地址空间分配。 硬件电路一旦确定,各芯片的地址范围实际上就已经确定,编程时只要给出所选择芯片的地址,就能对该芯片进行访问。以下结合上图,介绍IC1、IC2、IC3、IC4芯片地址范围的确定方法。

程序和数据地址均用16位,PO口确定低8位,P2口确定高8位。

如果P2.6=0、P2.5=1,选中IC2、IC4。地址线A15~AO与P2、PO对应关系如下:

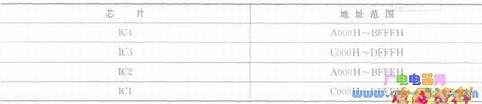

显然除P2.6、P2.5固定外,其他“×”位均可变。设无用位P2.7=1,当“×”各位全为0时,则为最小地址AOOOH;当“×”均为1时,则为最大地址BFFFH。所以IC21C4占用的地址空间为AOOOH~BFFFH共8 KB。同理IC1、IC3的地址范围为COOOH~DFFFH。4片存储器各自所占的地址空间见下表。

表 4片存储器芯片地址空间分配

IC2与IC4占用相同的地址空间,由于二者中一个为程序存储器,一个为数据存储器,3条控制线PSEN(的反)、WR(的反)、RD(的反)只能有一个有效。因此,即使地址空间重叠,也不会发生数据冲突。IC1与IC3也同样如此。

上面介绍的是采用线选法进行地址空间分配的示例,下面介绍采用译码器法进行地址空间分配的例子。

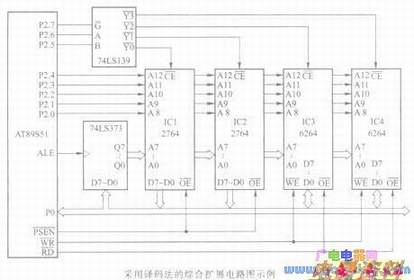

例2:采用译码法扩展2片8KB EPROM和2片8KB RAM。EPROM选用2764,RAM选用6264,共扩展4片芯片,扩展接口电路如下图所示。

图中,74LS139的4个输出端,YO(的反)~Y3(的反)分别连接4个芯片IC1、IC2、IC3、IC4的片选端。74LS139在对输入端译码时,YO(的反)~Y3(的反)每次只能有一位输出为0,其他3位全为l,输出为O的一端所连接的芯片被选中。

译码法地址分配,首先要根据译码芯片真值表确定译码芯片的输入状态,由此再判断其输出端选中芯片的地址。

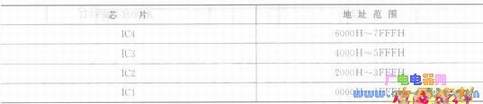

如下图所示,74LS139的输入端A、B、G(的反)分别接P2口的P2.5、P2.6、P2.7三端,G(的反)为使能端,低电平有效。当G(的反)=0、A=O、B=O时,输出端只有YO(的反)为O,Y1(的反)~Y3(的反)全为1,选中IC1。这样,P2.7、P2.6、P2.5全为O,P2.4~P2.O与PO.7~PO.O这13条地址线的任意状态都能选中IC1的某一单元。当13条地址线全为O时,为最小地址OOOOH;当13条地址线全为l时,为最大地址1FFFH,所以IC1芯片的地址范围为OOOOH~1FFFH。同理可确定电路中各个存储器的地址范围见下表。

表 4片存储器芯片地址空间分配

由上可见,译码法进行地址分配,各芯片的地址空间是连续的