Verilog-模块

模块是Verilog的模块的简单实例。

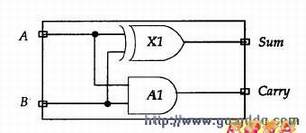

图2-1一个半加器电路的模块。

- moduleHalfAdder (A, B, Sum, Carry) ;

- input A, B; //输入

- output Sum, Carry;//输出

- assign #2 Sum = A ^ B;//赋值

- assign #5 Carry = A & B;//赋值

- endmodule

模块的名字是HalfAdder。模块有4个端口: 两个输入端口A和B,两个输出端口Sum和Carry。由于没有定义端口的位数, 所有端口大小都为1位;同时, 由于没有各端口的数据类型说明, 这四个端口都是线网数据类型。模块包含两条描述半加器数据流行为的连续赋值语句。从这种意义上讲,这些语句在模块中出现的顺序无关紧要,这些语句是并发的。每条语句的执行顺序依赖于发生在变量A和B上的事件。

在模块中,可用下述方式描述一个设计:

1) 数据流方式;

2) 行为方式;

3) 结构方式;

4) 上述描述方式的混合。

- 上一篇:Verilog-时延

- 下一篇:Verilog的主要描述能力