Verilog-设计模拟

Verilog HDL不仅提供描述设计的能力,而且提供对激励、控制、存储响应和设计验证的建模能力。激励和控制可用初始化语句产生。验证运行过程中的响应可以作为“变化时保存”或作为选通的数据存储。最后,设计验证可以通过在初始化语句中写入相应的语句自动与期望的响应值比较完成。

下面是测试模块To p的例子。该例子测试2 . 3节中讲到的FA S e q模块。

- ‘t i m e s c a l e 1 n s/1 n s

- m o d u l e T o p; // 一个模块可以有一个空的端口列表。

- r e g PA, PB, ;

- w i r e PCo, PSum;

- // 正在测试的实例化模块:

- FA_Seq F1(PA, PB, PCi, PSum, PC)o; // 定位。

- i n i t i a l

- b e g i n: O N L Y_O N C E

- r e g [3:0] P a l;

- / /需要4位, Pal才能取值8。

- f o r (P a l = 0; P al < 8; P a l = Pal + 1)

- b e g i n

- {PA, PB, PCi} = P a l;

- #5 $d i s p l a y (“PA, PB, PCi = %b%b%”b, PA, PB, PCi,

- “ : : : PCo, PSum=%b%b ”, PCo, PSum) ;

- e n d

- e n d

- e n d m o d u l e

在测试模块描述中使用位置关联方式将模块实例语句中的信号与模块中的端口相连接。也就是说,PA连接到模块FA S e q的端口A,P B连接到模块FA S e q的端口B,依此类推。注意初始化语句中使用了一个f o r循环语句,在PA、P B和P C i上产生波形。for 循环中的第一条赋值语句用于表示合并的目标。自右向左,右端各相应的位赋给左端的参数。初始化语句还包含有一个预先定义好的系统任务。系统任务$d i s p l a y将输入以特定的格式打印输出。

系统任务$ d i s p l a y调用中的时延控制规定$d i s p l a y任务在5个时间单位后执行。这5个时间单位基本上代表了逻辑处理时间。即是输入向量的加载至观察到模块在测试条件下输出之间的延迟时间。

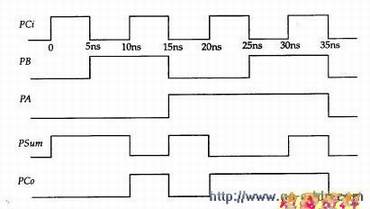

这一模型中还有另外一个细微差别。P a l在初始化语句内被局部定义。为完成这一功能,初始化语句中的顺序过程( b e g i n - e n d)必须标记。在这种情况下, ONLY O N C E是顺序过程标记。如果在顺序过程内没有局部声明的变量,就不需要该标记。测试模块产生的波形如图2 - 7显示。下面是测试模块产生的输出。

PA, PB, PCi = 000 ::: PCo, PSum = 00

PA, PB, PCi = 001 ::: PCo, PSum = 01

PA, PB, PCi = 010 ::: PCo, PSum = 01

PA, PB, PCi = 011 ::: PCo, PSum = 10

PA, PB, PCi = 100 ::: PCo, PSum = 01

PA, PB, PCi = 101 ::: PCo, PSum = 10

PA, PB, PCi = 110 ::: PCo, PSum = 10

PA, PB, PCi = 111 ::: PCo, PSum = 11

图2-7 测试模块To p执行产生的波形

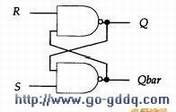

图2-8 交叉连接的

验证与交叉连接构成的R S F F模块的测试模块如图2 - 8所示。

- ` t i m e s c a l e 1 0 n s / 1 n s

- m o d u l e R S F F (Q, Qbar, R, S) ;

- o u t p u t Q, Qbar;

- i n p u t R, S;

- n a n d #1 (Q, R, Qbar) ;

- nand #1 (Qbar, S, Q,) ;

- / /在门实例语句中,实例名称是可选的。

- e n d m o d u l e

- m o d u l e T e s t;

- r e g TS, TR;

- w i r e TQ, TQb;

- / /测试模块的实例语句:

- RS_FF NSTA ( .Q(T Q), .S(T S), .R(T R), .Q b a r(T Q b));

- / /采用端口名相关联的连接方式。

- // 加载激励:

- i n i t i a l

- b e g i n:

- T R = 0;

- T S = 0;

- #5 T S = 1;

- #5 T S = 0;

- T R = 1;

- #5 T S = 1;

- T R = 0;

- #5 T S = 0;

- #5 T R = 1;

- e n d

- / /输出显示:

- i n i t i a l

- $m o n i t o r ("At time %t ," , $ t i m e,

- "TR = %b, TS=%b, TQ=%b, TQb= %b"T,R , TS, TQ, TQ)b ;

- e n d m o d u l e

RS_FF模块描述了设计的结构。在门实例语句中使用门时延;例如,第一个实例语句中的门时延为1个时间单位。该门时延意味着如果R或Qbar假定在T时刻变化,Q将在T+ 1时刻获得计算结果值。

模块Te s t是一个测试模块。测试模块中的R S F F用实例语句说明其端口用端口名关联方式连接。在这一模块中有两条初始化语句。第一个初始化语句只简单地产生T S和T R上的波形。这一初始化语句包含带有语句间时延的程序块过程赋值语句。

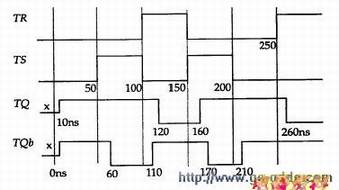

第二条初始化语句调用系统任务$m o n i t o r。这一系统任务调用的功能是只要参数表中指定的变量值发生变化就打印指定的字符串。产生的相应波形如图2 - 9所示。下面是测试模块产生的输出。请注意` t i m e s c a l e指令在时延上的影响。

图2-9 Te s t模块产生的波形

At time 0, TR=0, TS=0, TQ=x, TQb= x

At time 10, TR=0, TS=0, TQ=1, TQb= 1

At time 50, TR=0, TS=1, TQ=1, TQb= 1

At time 60, TR=0, TS=1, TQ=1, TQb= 0

At time 100, TR=1, TS=0, TQ=1, TQb= 0

At time 110, TR=1, TS=0, TQ=1, TQb= 1

At time 120, TR=1, TS=0, TQ=0, TQb= 1

At time 150, TR=0, TS=1, TQ=0, TQb= 1

At time 160, TR=0, TS=1, TQ=1, TQb= 1

At time 170, TR=0, TS=1, TQ=1, TQb= 0

At time 200, TR=0, TS=0, TQ=1, TQb= 0

At time 210, TR=0, TS=0, TQ=1, TQb= 1

At time 250, TR=1, TS=0, TQ=1, TQb= 1

At time 260, TR=1, TS=0, TQ=0, TQb= 1

后面的章节将更详细地讲述这些主题。

- 上一篇:Verilog HDL中的标识符

- 下一篇:Verilog-混合设计描述方式