使用ModelSim-Altera对NiosII进行仿真

初学者可能会遇到这样的问题,在Run As Nios II Hardware下方,看到Run As Nios II ModelSim就觉得很奇怪,Nios II明明是嵌入式系統,怎么能用ModelSim仿真呢?

使用環境:Qus II 7.2 SP3 + Nios II EDS 7.2 SP3 + ModelSim-Ara 6.1g + DE2(Cyclone II EP2C35F627C6)

用ModelSim对数字系统作仿真,这个大家可能都很熟悉。Nios II虽然是个嵌入式系统,但毕竟基于技术,所以比ARM这类hardcore多了使用ModelSim仿真的方式。这也是Altera四大天王(Quartus II、Nios II EDS、ModelSim-Altera、 Builder)中的三大天王首次同台演出。

Altera在文件中,有谈到如何用ModelSim-Altera对Nios II作仿真,不过一如以往,Altera的文件要在DE2能动,还是得做不少修改。

Quartus II与SOPC Builder部分

Step 1:

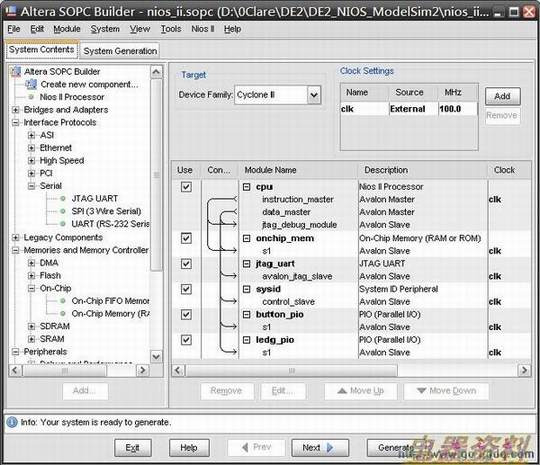

文件中的那个系统并不适合DE2,用了一定不能动,所以就自己建立一个最简单的Nios II系统。为了要简单,就先使用on memory与g与button就好,其他IP都先别用,以减少失败的变因。

Step 2:

UART设定

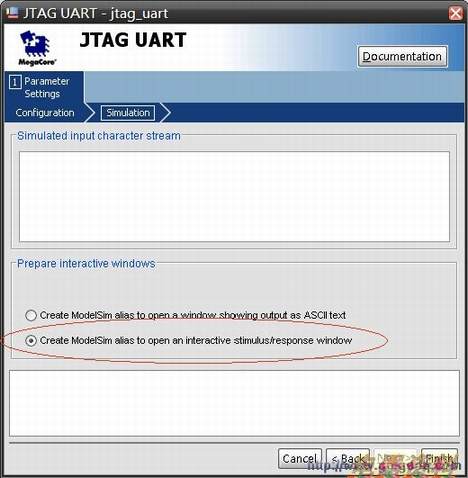

使用ModelSim-Altera仿真后,对于C的printf()要怎么显示呢?这要对JTAG UART做设定。

Step 3:

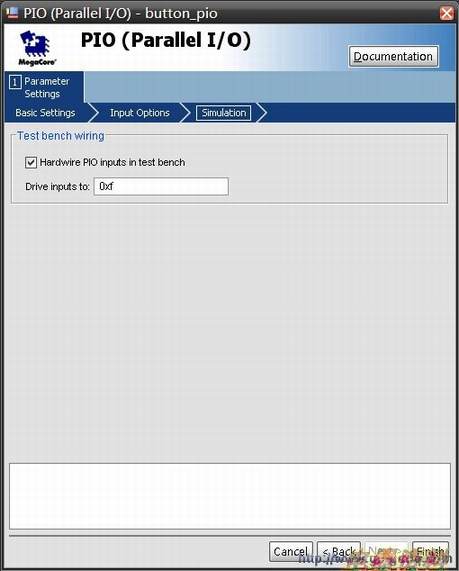

Button本来是在runtime由user去决定,若你想在testbench就模拟user的按键,可在此设定,此步骤并非必须,只是demo可藉由此方式设定PIO的初始值。

Step 4:

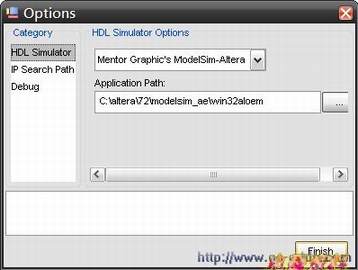

在SOPC Builder设定ModelSim-Altera路径

Tools -> Options -> Category:HDL Simulator

Step 5:

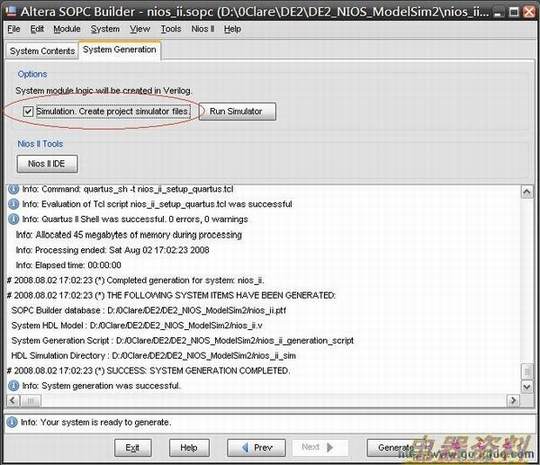

记得要将『Simulation. Create project simulator files』打勾。

Step 6:

DE2_NIOS_ModelSim2.v / Verilog

1 /*

2 (C) OOMusou 2008 //oomusou.cnblogs.com

3

4 Filename : DE2_NIOS_ModelSim2.v

5 Compiler : Quartus II 7.2 SP3

6 Description : Demo how to simulate Nios II by ModelSim-Altera

7 Release : 08/02/2008 1.0

8 */

9

10 module DE2_NIOS_ModelSim2 (

11 input CK_50,

12 input [3:0] KEY,

13 output [8:0] LEDG

14 );

15

16 wire CPU_CLK;

17 wire CPU_RESET;

18

19 Reset_Delay delay1 (

20 .iRST(KEY[0]),

21 .LK(CLOCK_50),

22 .oRESET(CPU_RESET)

23 );

24

25 SDRAM_ PLL1 (

26 .inclk0(CLOCK_50),

27 .c1(CPU_CLK)

28 );

29

30 nios_ii u0 (

31 .clk(CPU_CLK),

32 .reset_n(CPU_RESET),

33 .in_port_to_the_button_pio(KEY),

34 .out_port_from_the_ledg_pio(LEDG)

35 );

36

37 endmodule

25行

SDRAM_PLL PLL1 (

.inclk0(CLOCK_50),

.c1(CPU_CLK)

);

别被SDRAM_PLL吓到了,只是借用这个PLL产生100 M的clock给Nios II用,你也可以自己重新产生一个100 Mhz的clock而不用SDRAM_PLL。

Quartus II与SOPC Builder部分已经完成,编译后可烧进DE2。

(