Verilog-initial语句

initial语句:在仿真中只执行一次,用于初始化变量,描述一次性行为,在仿真时刻0开始执行。

下面是initial语句的示例:

- `timescale 1ns/1ns

- moduleTest(Pop,Pid);

- outputPop,Pid;

- regPop,Pid;

- initial

- begin

- Pop=0;//语句1。

- Pid=0;//语句2。

- Pop=#51;//语句3。

- Pid=#31;//语句4。

- Pop=#60;//语句5。

- Pid=#20;//语句6。

- end

- endmodule

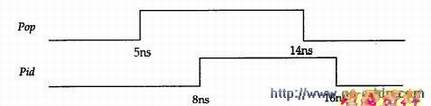

这一模块产生如图2-5所示的波形。initial语句包含一个顺序过程。这一顺序过程在0ns时开始执行,并且在顺序过程中所有语句全部执行完毕后,initial语句永远挂起。这一顺序过程包含带有定义语句内时延的分组过程赋值的实例。语句1和2在0ns时执行。第三条语句也在0时刻执行,导致Pop在第5ns时被赋值。语句4在第5ns执行,并且Pid在第8ns被赋值。同样,Pop在14ns被赋值0,Pid在第16ns被赋值0。第6条语句执行后,initial语句永远被挂起。第8章将更详细地讲解initial语句。

图2-5

- 上一篇:Verilog-always语句

- 下一篇:Verilog-assign语句